# Personal Computer **TZ - 30B** RS-232C SERIAL INTERFACE

Personal Computer MZ-80B

# RS-232C Serial Interface Card Model: MZ-8BI03 Technical Manual

Copyright<sup>©</sup> by SHARP CORPORATION

## Contents

| 1. General Information 2                    |

|---------------------------------------------|

| 2. Specifications                           |

| 3. Cautions for Handling 4                  |

| 4. Method of Operation 5                    |

| Arrangement of switches and jumper chips 5  |

| Setting port address 6                      |

| Setting baud rate for each channel 8        |

| Modes of connector signals 9                |

| Setting Channel A 11                        |

| Setting Channel B 12                        |

| Installation of the inferface card 13       |

| Setting the card for delivery 14            |

| 5. Electrical Characteristics of Signals 15 |

| Direction of signals for RS-232C 15         |

| Direction of signals for current loop 15    |

| Signal level with RS-232C interface         |

| Current loop 17                             |

| 6. Programming 19                           |

| Interrupts                                  |

| 7. Z-80-SIO Registers                       |

| Write registers                             |

| Read registers 43                           |

| 8. Sample programs 51                       |

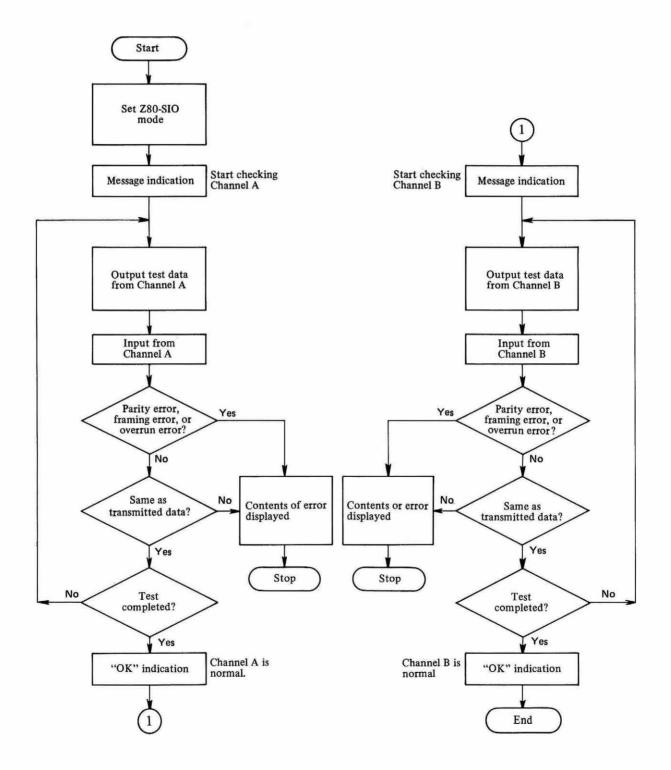

| Self-diagnosis program 51                   |

| Setting jumper blocks on the card 51        |

| Flow chart of Self-Diagnosis program        |

| Program by BASIC/PASCAL language            |

| 9. BASIC SB-6511                            |

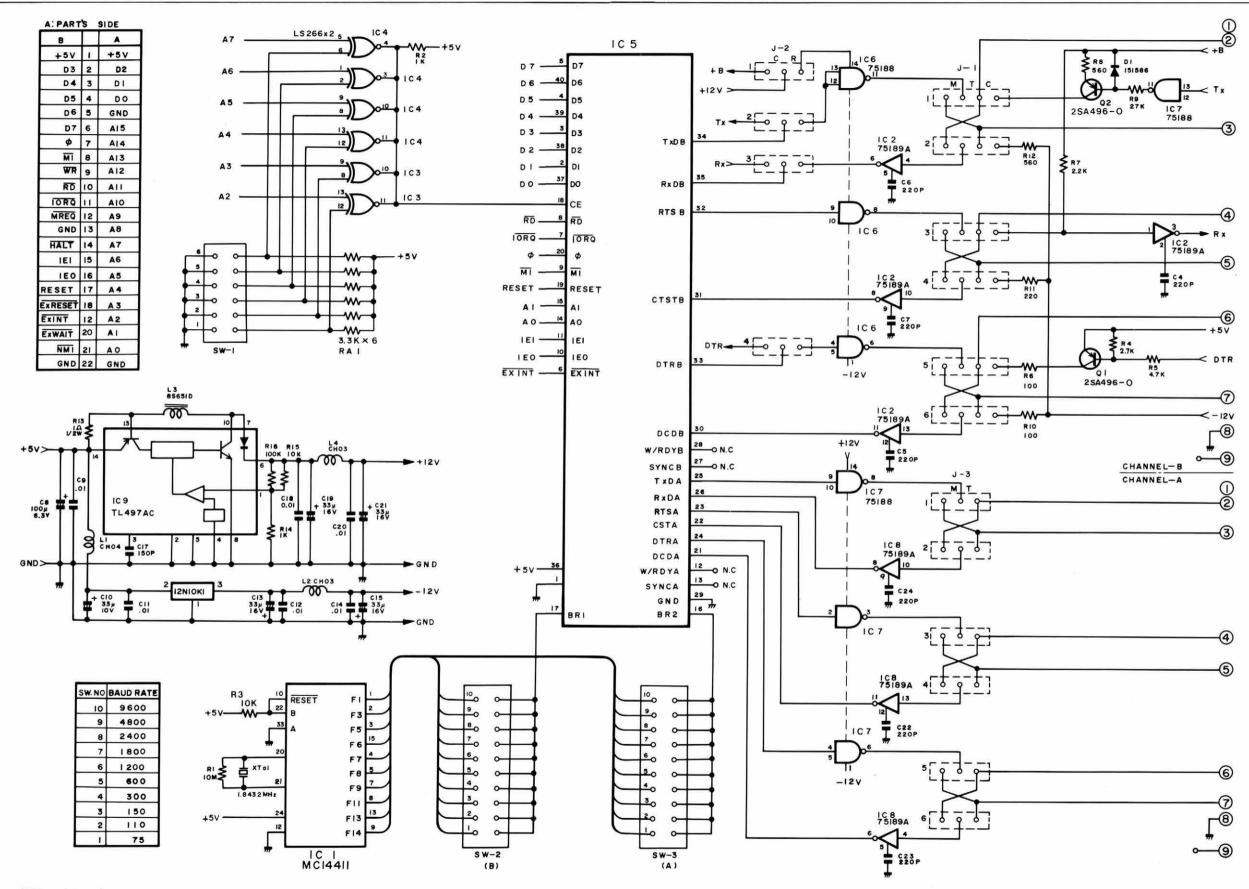

| 10. Circuit Diagram                         |

|                                             |

## **1. General Information**

#### Introduction

There are two methods of data communication between computer and external equipment: 8-bit parallel and bit serial.

The serial interface card MZ-8BI03 (hereinafter referred to as "interface card") permits data communication by the bit serial method. This interface card is manufactured in accordance with EIA RS-232C (the Electronic Industries Association RS-232C), and used for data communication with other equipment having interface based on RS-232C.

#### Functions of this interface card

The interface card has the following functions.

- 1. One card has two channels, each of which is capable of transmitting/receiving data independently.

- 2. One of the ten baud rates can be selected by operating the switch on the card. Baud rates can be set independently for the two channels.

- 3. Output connector signals to external equipment can be in either terminal mode or modem mode through the operation of the jumper chip.

- 4. This interface card can be used as 20mA current loop for one channel.

#### Applications

Equipped with the above-mentioned functions, the interface card has a variety of applications. Some applications of this very versatile serial interface card are shown below.

- 1. Data communication between computers on telephone line via acoustic couplers

- 2. Printer

- 3. Plotter

- 4. Digitizer

- 5. Graphic display

- 6. Card reader

- Magnetic tape equipment

# 2. Specifications

| Communication mehod:   | Asynchronous                                                        |

|------------------------|---------------------------------------------------------------------|

| Standard:              | In compliance with EIA RS-232C                                      |

| Control LSI:           | Z-80SIO/0                                                           |

| Number of channels:    | 2 (Channel A and Channel B)                                         |

| 20mA current loop:     | Changeover is allowed for one channel (Channel B)                   |

| Baud rate:             | Can be set independently for the two channels (Manual setting using |

|                        | switch)                                                             |

| Number of baud rates:  | 10 (75, 110, 150, 300, 600, 1200, 1800, 2400, 4800, 9600 baud)      |

| Character length:      | 5, 6, 7 or 8 bits (Selection by software)                           |

| Parity bit:            | Odd, none, or even                                                  |

| Stop bit:              | 1, 1½, or 2                                                         |

| Mode:                  | Either terminal mode or modem mode can be selected for each channel |

|                        | (through the use of jumper chip).                                   |

| Interrupt:             | Z-80 vector interrupt can be used.                                  |

| Port address:          | Manual setting with switch                                          |

| Operating temperature: | $0^{\circ}C \sim 50^{\circ}C$                                       |

| Storage temperature:   | −25°C ~ 80°C                                                        |

(Note) The above-mentioned specifications may be changed in the future for improvement of the product.

## 3. Cautions for Handling

- This interface card has been especially designed for Sharp personal computer MZ-80B. Do not use this card for other equipment, or destruction of circuit or other troubles may be caused.

- Since the interface has NMOS, CMOS, and other highly integrated ICs incorporated in it, take adequate precautions in handling the card so that no static electricity will be generated. Otherwise, the ICs may be destroyed.

- When pulling the card out of the expansion unit, do NOT pull the signal cable. Otherwise, disconnection of wire may be caused.

- Set the switch, jumper, etc. on the card only when power is turned off.

- Do not turn ON more than one switches at a time for baud rate setting. Otherwise, the ICs may be destroyed.

- The manufacturer will not be held responsible for troubles resulting from the alteration of the circuit by the user.

- For storage, protect this interface card from static electricity, for example, by putting it in an electrically conductive bag.

- Do not leave the interface card in the following places.

- Place with too much/little humidity

- Place exposed to direct sunlight

- Dusty place

- · Excessively hot/cold place

- Place with a lot of vibration

## 4. Method of Operation

## Arrangement of switches and jumper chips

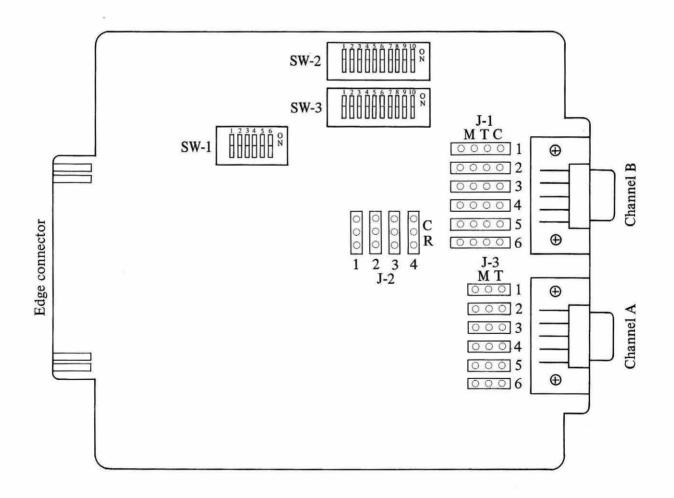

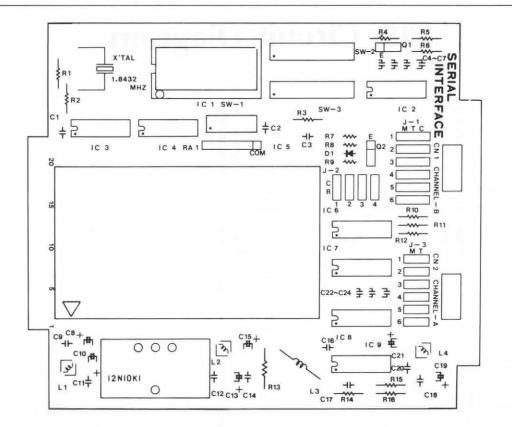

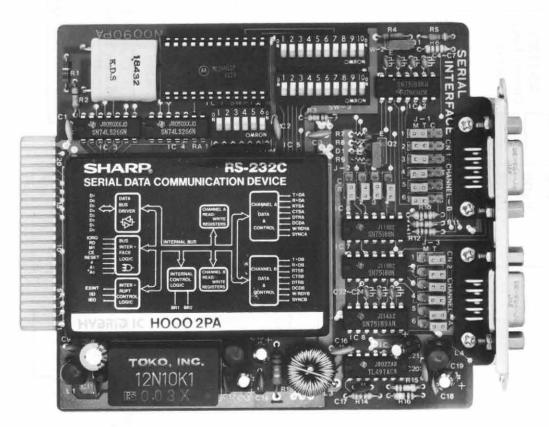

Before using this card, the switches and jumpers on the card must be set first. Fig. 4-1 shows the positions of the switches and jumpers.

| Switch SW-1:      | Used for setting port address                                |

|-------------------|--------------------------------------------------------------|

| Switch SW-2:      | Used for setting baud rate for Channel B                     |

| Switch SW-3:      | Used for setting baud rate for Channel A                     |

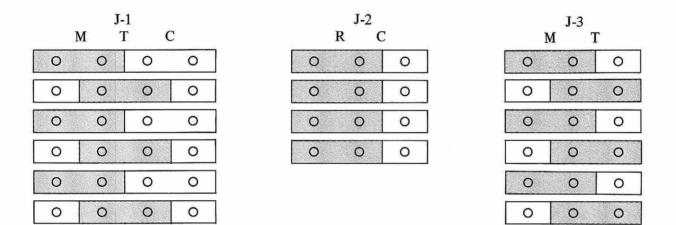

| Jumper block J-1: | Jumper for mode selection for Channel B                      |

| Jumper block J-2: | Jumper for selection of RS-232C/current loop (for channel B) |

| Jumper block J-3: | Jumper for mode selection for Channel A                      |

|                   |                                                              |

#### Fig. 4-1. Arrangement of Switches and Jumpers

## Setting port address

The Z80-CPU outputs 8-bit port address. Since this card uses 4 sequential port addresses, the port address can be set by setting upper 6 bits of the 8-bit address signal using the switch (SW-1).

As shown in Table 4-1, the upper 6 bits  $(A_2 \sim A_7)$  of the 8-bit address signal can be selected arbitarily.

| Address bit    | Segment of switch SW-1 | Manufacturer's setting | Comment                           |

|----------------|------------------------|------------------------|-----------------------------------|

| A <sub>7</sub> | 6                      | OFF                    |                                   |

| A <sub>6</sub> | 5                      | ON                     |                                   |

| $A_5$          | 4                      | OFF                    |                                   |

| $A_4$          | 3                      | OFF                    | These bits can be set arbitarily. |

| A <sub>3</sub> | 2                      | ON                     |                                   |

| A <sub>2</sub> | 1                      | ON                     |                                   |

| A <sub>1</sub> |                        | -                      | Channel select                    |

| A <sub>0</sub> | -                      | -                      | Control or Data Select            |

Table 4-1. Switch for Setting Port Address

The correspondence between the switching positions of the switch SW-1 and logic levels is as shown below. The address of this interface card is the port address whose logic level coincides with that of the switch SW-1.

| Switching position | Logic level |

|--------------------|-------------|

| ON                 | 0           |

| OFF                | 1           |

Table 4-1 shows the state of the switch SW-1 as set by the manufacturer for delivery. In this case, the port addresses are B0H, B1H, B2H, and B3H.

Address bit  $A_1$  is assigned for selecting channels for Z80-SIO whereas address bit  $A_0$  is assigned for selection of control word or data.

| A <sub>1</sub> | A <sub>0</sub> | Selection              |  |  |  |

|----------------|----------------|------------------------|--|--|--|

| 0              | 0              | Channel A/Data         |  |  |  |

| 0              | 1              | Channel A/Control word |  |  |  |

| 1              | 0              | Channel B/Data         |  |  |  |

| 1              | 1              | Channel B/Control word |  |  |  |

ON condition OFF condition Switching condition

### Setting baud rate for each channel

The interface card has two channels (Channel A and Channel B), for each of which baud rate can be set independently. This operation can be carried out by selecting the switches SW-2 and SW-3 on the card. One out of the 10 baud rates can be selected.

| Switch SW-2 | For setting baud rate for Channel B |

|-------------|-------------------------------------|

| Switch SW-3 | For setting baud rate for Channel A |

The setting methods are the same for both channels. Turn on the switch corresponding to the desired baud rate and turn off the other switches. The correspondence between the segments of the switches and baud rates is shown in Table 4-2.

| D1 D.4.   |     | Segments of switches SW-2 and SW-3 |     |     |     |     |     |     |     |      |

|-----------|-----|------------------------------------|-----|-----|-----|-----|-----|-----|-----|------|

| Baud Rate | 1   | 2                                  | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10   |

| 75 baud   | ON  | OFF                                | OFF | OFF | OFF | OFF | OFF | OFF | OFF | OFF  |

| 110       | OFF | ON                                 | OFF  |

| 150       | OFF | OFF                                | ON  | OFF  |

| 300       | OFF | OFF                                | OFF | ON  | OFF | OFF | OFF | OFF | OFF | OFF  |

| 600       | OFF | OFF                                | OFF | OFF | ON  | OFF | OFF | OFF | OFF | OFF  |

| 1200      | OFF | OFF                                | OFF | OFF | OFF | ON  | OFF | OFF | OFF | OFF  |

| 1800      | OFF | OFF                                | OFF | OFF | OFF | OFF | ON  | OFF | OFF | OFF  |

| 2400      | OFF | OFF                                | OFF | OFF | OFF | OFF | OFF | ON  | OFF | OFF  |

| 4800      | OFF | OFF                                | OFF | OFF | OFF | OFF | OFF | OFF | ON  | OFF  |

| 9600      | OFF | OFF                                | OFF | OFF | OFF | OFF | OFF | OFF | OFF | ON - |

Table 4-2. Setting Baud Rates

(Caution) In setting baud rate, only one of the 10 segments of the switch SW-2 or SW-3 must be turned ON. Turning ON 2 or more segments will cause destruction of the ICs. After setting, confirm that only one segment of each switch is turned ON.

2.16

### Modes of connector signals

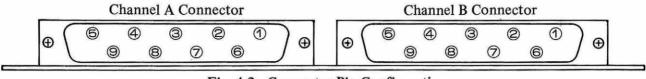

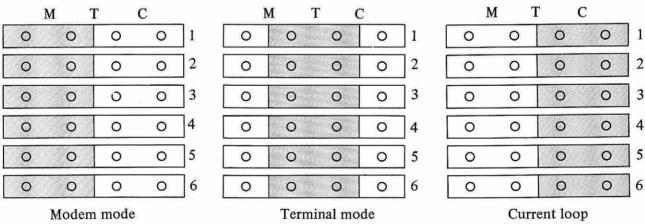

This interface card has two 9-pin connectors as shown in Fig. 4-2.

Fig. 4-2. Connector Pin Configuration

By changing the wiring of the jumper blocks J-1, J-2, J-3 on the card, signals for each connector pin can be changed. Through this operation, the channels can be set in three different states: terminal mode, modem mode, and current loop.

Terminal and modem modes are in compliance with RS-232C standard. In both modes, binary signals are transmitted by voltage levels.

Current loop is not included in the RS-232C standard, but is adopted in ASR-33 manufactured by Teletype Corporation. By this method, binary signals are transmitted with intermittent 20mA current.

The modes available for each channel are given in Table 4-3.

| Mode          | Channel A     | Channel B |

|---------------|---------------|-----------|

| Terminal mode | Available     | Available |

| Modem mode    | Available     | Available |

| Current loop  | Not available | Available |

Table 4-3. Channel Mode

The correspondence between connector pins and signals in different modes is shown in Table 4-4. For connector pin numbers, refer to Fig. 4-2.

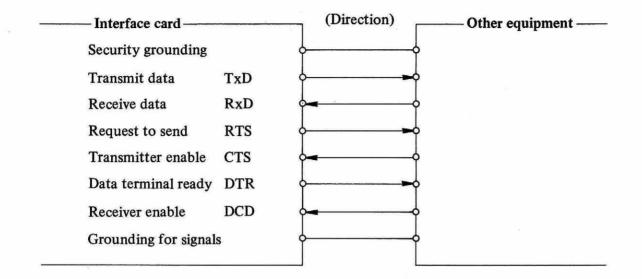

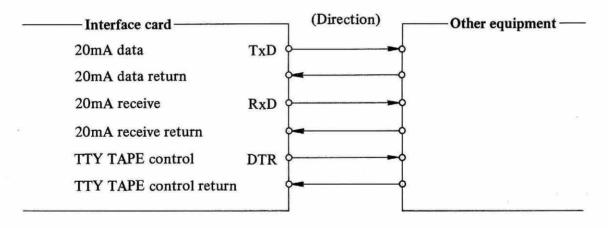

| Connector pin No. | Terminal mode                                   | Modem mode                                      | Current loop                |  |

|-------------------|-------------------------------------------------|-------------------------------------------------|-----------------------------|--|

| 1                 | Security grounding                              | Security grounding                              | Security grounding          |  |

| 2                 | Transmit data TxD                               | Receive data RxD                                | 20mA data TxD               |  |

| 3                 | Receive data RxD                                | Transmit data TxD                               | 20mA data return            |  |

| 4                 | Request to send<br>RTS                          | Clear to send CTS<br>(Transmitter enable)       | 20mA receive RxD            |  |

| 5                 | Clear to send CTS<br>(Transmitter enable)       | Request to send<br>RTS                          | 20mA receive return         |  |

| 6                 | Data terminal<br>ready DTR                      | Data carrier detect<br>DCD<br>(Receiver enable) | TTY TAPE control return DTR |  |

| 7                 | Data carrier detect<br>DCD<br>(Receiver enable) | Data terminal<br>ready DTR                      | TTY TAPE control return     |  |

| 8                 | Grounding for signals                           | Grounding for signals                           | Grounding for signals       |  |

| 9                 | NC                                              | NC                                              | NC                          |  |

Table 4-4. Signal Configuration

In the terminal mode, transmit data are connected to pin No. 2. However, in the modem mode, receive data are connected to pin No. 2, thus creating a reverse flow of signals. The directions of each connector pin are opposite in the terminal and modem modes. This feature can be utilized in the following way.

- Terminal mode is selected for connection with acoustic coupler

- Modem mode is selected for connection with printers, plotters, etc. equipped with RS-232C interface.

Of course, there are some exceptions. Therefore, read the instruction manuals of individual equipment.

## Setting Channel A

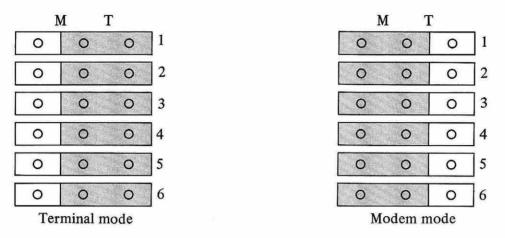

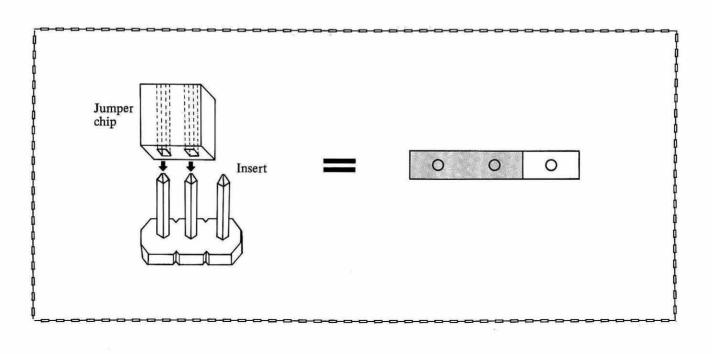

The mode of Channel A can be set by changing jumper wiring of the jumper block J-3. Terminal mode can be selected by short-circuiting all pairs of terminals marked "T" by inserting jumper chips between them as illustrated in Fig. 4-3. Modem mode can be selected by doing the same for pairs of terminals marked "M".

Fig. 4-3 Setting Modes for Channel A (Jumper block J-3)

Incidentally, Channel A is set at terminal mode for delivery.

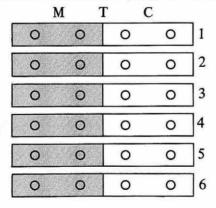

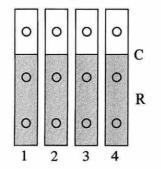

### Setting Channel B

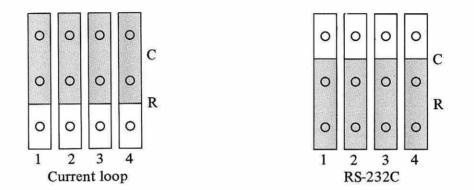

Either RS-232C or current loop must be selected for Channel B. For this purpose, change the jumper wiring of the jumper block J-2. Current loop can be selected by short-circuiting all pairs of terminals marked "C" with the use of jumper chips, and RS-232C can be selected by doing the same for all apirs of terminals marked "R", as shown in Fig. 4-4.

Fig. 4-4 Jumper Block J-2

Incidentally, the jumper block J-2 is set at RS-232C side for delivery.

Next, Channel B can be set at terminal mode, modem mode, or current loop by manipulating the jumper block J-1. The wiring of jumper chips is illustrated in Fig. 4-5.

Fig. 4-5 Jumper Block J-1

The jumper block J-1 is set at modem mode at the time of delivery.

## Installation of the interface card

This card is designed for installation in Sharp personal computer MZ-80B. Install the card in the following procedure.

- 1. Set port address, baud rate, and mode of each channel. For this purpose, set the switches and jumper blocks on the card.

- Insert this card into the slot of the MZ-80B expansion unit. There are 6 slots in the expansion unit. Use any one of slot Nos. 1, 2, 4, and 5. For the method of insertion and the installation of expansion unit, refer to the Owner's Manual for MZ-80B.

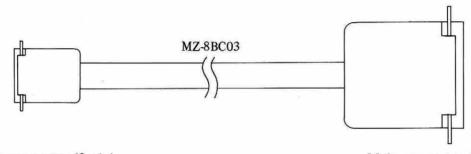

- 3. Connect the card with other equipment, using signal cable. Signal cable MZ-8BC03 to be exclusively used for this card is sold separately. Fix both ends of the connector connection on the card side, using screws.

Male connector (9 pin) JAE DE-9P or equivalent

Male connector (25 pin) JAE DB-25P or equivalent

Fig. 4-6 Signal Cable

## Setting the card for delivery

• Port address (SW-1): B0H, B1H, B2H, B3H

| Switch segmen      | ıt    | 1      | 1   | 2   | 3   | 4   |     | 5   | 6   |    |

|--------------------|-------|--------|-----|-----|-----|-----|-----|-----|-----|----|

| Switch positio     | n     | 0      | N   | ON  | OFF | OF  | F   | ON  | OFF |    |

| Baud rate (SW-2, S | W-3): | 9600 b | aud |     |     |     |     |     |     |    |

| Switch segment     | 1     | 2      | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10 |

| Switch position    | OFF   | OFF    | OFF | OFF | OFF | OFF | OFF | OFF | OFF | ON |

• Terminal mode for Channel A (J-3): Terminal mode

| N | A ' | Г | _ |

|---|-----|---|---|

| 0 | 0   | 0 | 1 |

| 0 | 0   | 0 | 2 |

| 0 | 0   | 0 | 3 |

| 0 | 0   | 0 | 4 |

| 0 | 0   | 0 | 5 |

| 0 | 0   | 0 | 6 |

• Terminal mode for Channel B (J-1): Modem mode

• RS-232C/current loop selection for Channel B (J-2): RS-232C

## 5. Electrical Characteristics of Signals

## **Direction of signals for RS-232C**

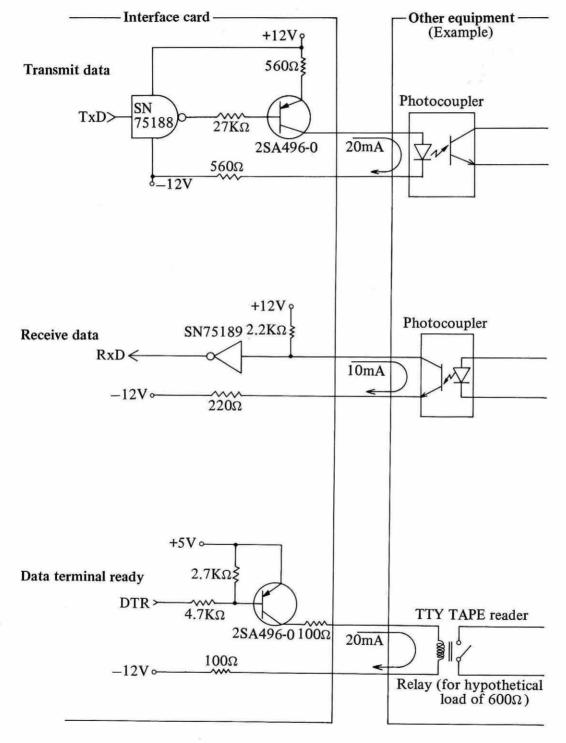

## Direction of signals for current loop

## Signal level with RS-232C interface

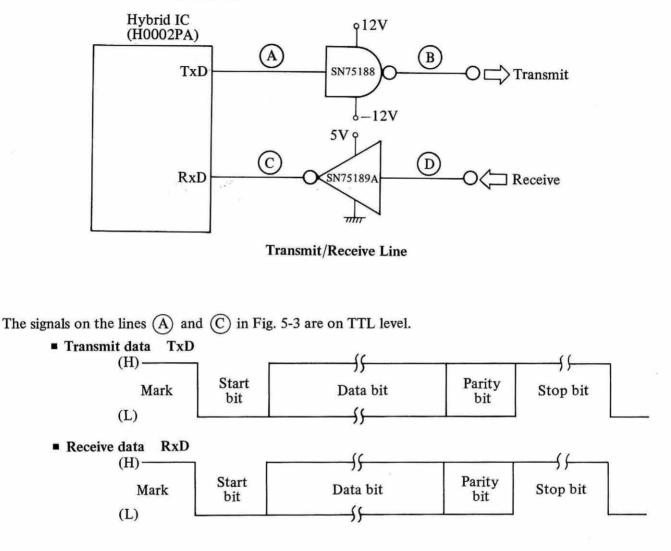

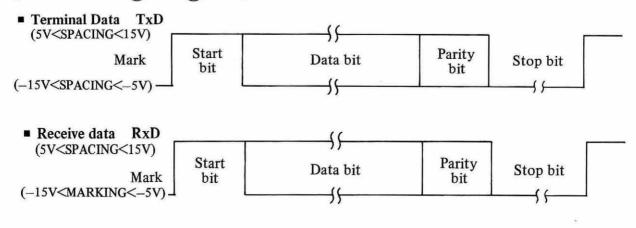

The signal levels (voltage levels) and polarities of transmit data (TxD) and receive data (RxD) with RS-232C interface are as follows.

The signals on the lines (B) and (D) in Fig. 5-3 are on RS-232C level.

## **Current** loop

Current loop permits transmission/receiving of signals on logic levels 1 and 0, depending on the presence/absence of current. The direction of current flow is illustrated below.

Note: Since current value varies depending on load, typical values are shown here.

## 6. Programming

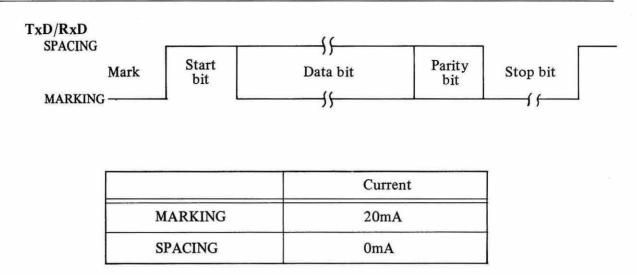

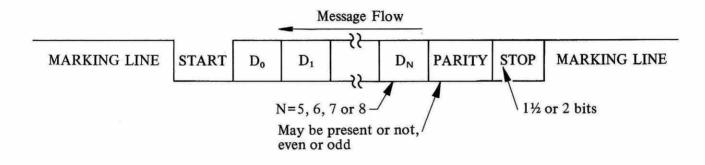

The interface card transmits data by the asynchronous transmission method. In the asynchronous data communication, a datum is composed of 4 parts: start bit, character length, parity bit, and stop bit, as shown in Fig. 6-1.

Fig. 6-1 Asynchronous Message Format

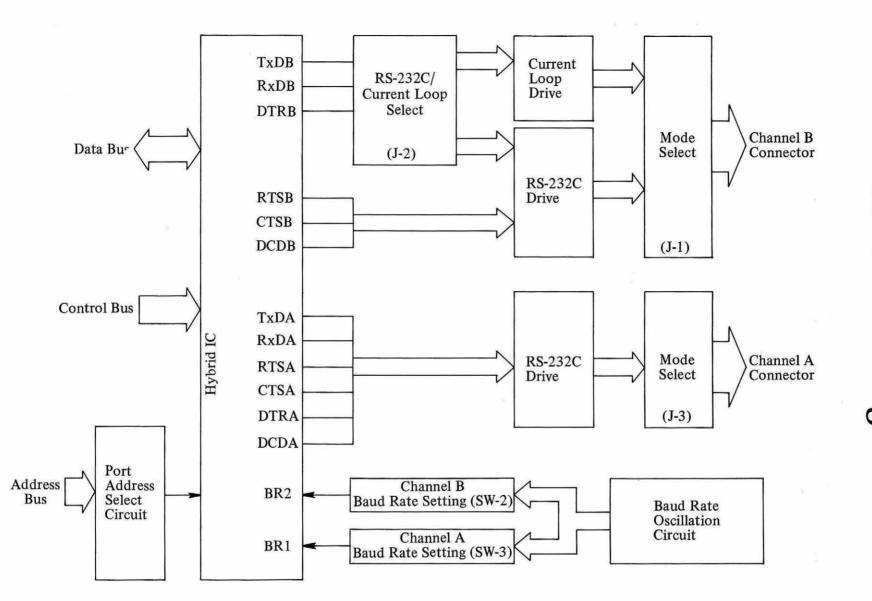

The hybrid IC (H0002PA) converts 8-bit parallel data into the message format as shown in Fig. 6-1 to transmit the data according to the predetermined baud rate, and, conversely, receives data, while checking the contents of errors, and convert them into 8-bit parallel data.

The hybrid IC consists of Z80A-SIO/0 logic, interrupt vector logic, bus interface logic, etc., and can be directly connected with Z80A-CPU bus. Further, the direct connection eliminates the necessity of a logic to return interrupt vector in the interrupt mode 2 of Z80-CPU. Fig. 6-2 shows the block diagram of the hybrid IC.

Therefore programming of the hybrid IC can be conceived in the same way as in the case of Z80A-SIO programming. The hybrid IC has two channels (Channel A and Channel B), each of which has a read register and a write register for control of the channel. Table 6-1 shows the relationship between port addresses and transmit/receive data/register, and Table 6-2 shows the registers of each channel.

#### Fig. 6-2 Block Diagram of Hybrid IC

20

| 700 CDU         | A                     | ldress         | Emetion                       |  |  |  |  |

|-----------------|-----------------------|----------------|-------------------------------|--|--|--|--|

| Z80-CPU command | <b>A</b> <sub>1</sub> | A <sub>0</sub> | Function                      |  |  |  |  |

| IN              | L                     | L              | Channel A receive data read   |  |  |  |  |

| IN              | L                     | н              | Channel A register read       |  |  |  |  |

| IN              | н                     | L              | Channel B receive data read   |  |  |  |  |

| IN              | н                     | н              | Channel B register read       |  |  |  |  |

| OUT             | L                     | L              | Channel A transmit data write |  |  |  |  |

| OUT             | L                     | н              | Channel A register write      |  |  |  |  |

| OUT             | н                     | L              | Channel B transmit data write |  |  |  |  |

| OUT             | Н                     | Н              | Channel B register write      |  |  |  |  |

Table 6-1,

Table 6-2. Read/Write Registers

| Channel A | Write register | WR0 | WR1 | -   | WR3 | WR4 | WR5 | WR6 | WR7 |

|-----------|----------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Channel A | Read register  | RR0 | RR1 |     |     |     |     |     |     |

| ci 1 D    | Write register | WR0 | WR1 | WR2 | WR3 | WR4 | WR5 | WR6 | WR7 |

| Channel B | Read register  | RR0 | RR1 | RR2 |     | •   |     |     |     |

In order to carry out transmission/receiving of data via this interface card, the following three programs (mode setting, input, and output) are required basically. For details, refer to the description of the registers which will be given later.

#### Mode setting program

Particulars of asynchronous data communication must be set in the first place. Mode setting includes the following.

- Magnification of clock rate (Set at x 16)

- Number of stop bits (1, 1½, or 2)

- Presence/absence of parity bit

- Designation of odd or even parity, if any

- Transmit/receive character length (5, 6, 7, or 8 bits)

#### Input program

Program to read the data received by the hybrid IC.

| Error check: | Checks $D_6$ , $D_5$ , and $D_4$ of read register PR1.        |

|--------------|---------------------------------------------------------------|

| Data read:   | Checks $D_0$ of read register RR0, and reads data if it is 1. |

#### Output program

Program to write data to be transmitted to the hybrid IC. This program checks  $D_9$  of the register RR0 and writes data it is 1. After that, start bit, parity bit, and stop bit are automatically added for transmission.

#### Example of control program

A list by assembler language is shown as an example of control program using this interface card.

| Set port address   | S   |

|--------------------|-----|

| Channel A/data:    | BOH |

| Channel A/control: | B1H |

| Channel B/data:    | B2H |

| Channel B/control: | B3H |

#### Mode setting parameters

Clock rate:x 16Stop bit:2 bitsParity:PresentOdd/even of parity:EvenTransmit/receivecharacter length:8 bitsDTR, RTS:Set

\*\* Z80 ASSEMBLER SB-7201 (SIF-ROUTINE) PAGE 01 01 0000 02 0000 . 03 0000 ; Serial I/F Subroutine for MZ-8BI03 on MZ-80B 04 0000 : 05 0000 06 0000 ; 07 F000 ORG FOOOH 08 F000 ; 09 F000 ;\*\*\* Port Address Equation \*\*\* 10 F000 : 11 F000 P CHADT: EQU BOH ; channel A data port 12 F000 P CHACT: EQU B1H ; channel A control port 13 F000 P CHBDT: EQU B2H ; channel B data port 14 F000 P CHBCT: EQU **B**3H ; channel B control port 15 F000 5 16 F000 ;\*\*\* Parameter \*\*\* 17 F000 ; 18 F000 WR: ENT 19 F000 18 DEFB 188 ; channel reset 20 F001 10 DEFB 10H : EXT/STATUS reset 21 F002 10 DEFB 10H ; EXT/STATUS reset 22 F003 04 WR4: DEFB 4 ; register NO. 23 F004 4F DEFB 4FH ; x16,2stop,EV,PE 24 F005 05 WR5: DEFB 5 ; register NO. 25 F006 EA DEFB EAH \$ DTR,TxDT=8,TxEN,RTS 26 F007 03 WR3: DEFB 3 ; register NO. 27 F008 C0 : RxDT=8 COH DEFB 28 F009 1 29 F009 MODE: ENT ; mode set 30 F009 0EB1 C+CHACT LD ; CH.A port adr. load 31 FOOB 0609 LD B . 9 32 FOOD 2100F0 HL, WR LD 33 F010 EDB3 OTIR ; parameter transfer 34 F012 0EB3 LD C+CHBCT ; CH.B port adr. load 35 F014 0609 LD B,9 36 F016 2100F0 LD HL + WR 37 F019 EDB3 OTIR ; parameter transfer 38 F01B 3E03 A+3 LD ; CH.A RxEN 39 F01D D3B1 OUT (CHACT),A 5 40 F01F 3A08F0 LD A+ (WR3+1) . 41 F022 F601 OR 1 42 F024 D3B1 OUT (CHACT),A 43 F026 3E03 LD A + 3 ; CH.B RXEN 44 F028 D3B3 OUT (CHBCT),A 45 F02A 3A08F0 LD A, (WR3+1) 46 F02D F601 OR 1 47 F02F D3B3 OUT (CHBCT),A 48 F031 C9. RET 49 F032 SKP н

à

1

|         | **           | Z 80 | ASSEMBLER    | SB-7 | 7201       | <si< th=""><th>F-ROUT</th><th>[INE &gt;</th><th>PAGE</th><th>02</th><th></th><th></th><th></th><th></th><th></th></si<> | F-ROUT      | [INE >   | PAGE   | 02          |        |                 |        |         |  |

|---------|--------------|------|--------------|------|------------|-------------------------------------------------------------------------------------------------------------------------|-------------|----------|--------|-------------|--------|-----------------|--------|---------|--|

| 01      | F032         |      |              |      | ;          |                                                                                                                         |             |          |        |             |        |                 |        |         |  |

| 02      | F032         |      |              |      |            | INF                                                                                                                     | UT ROU      | ITINE    |        |             |        |                 |        |         |  |

|         | F032         |      |              |      | ;          |                                                                                                                         | F=0 :       |          |        |             |        |                 |        |         |  |

|         | F032         |      |              |      | ;          |                                                                                                                         | F=1 :       |          |        |             | 110100 | الد در مدر      |        |         |  |

|         | F032         |      |              |      | ;          | (1                                                                                                                      |             |          |        | DR<br>Error |        |                 |        |         |  |

|         | F032         |      |              |      | ;          |                                                                                                                         |             |          |        | ERROR       |        |                 |        |         |  |

|         | F032         |      |              |      | ;          |                                                                                                                         |             |          |        | ERROR       |        | NO              |        |         |  |

| 09      | F032         |      |              |      | ;          |                                                                                                                         |             |          |        |             |        |                 |        |         |  |

|         | F032         |      |              |      | INER@      | :                                                                                                                       | ENT         |          |        |             | ;      | error           | code   | buffer  |  |

| 1211222 | F032         |      |              |      | -          |                                                                                                                         | DEFS        | 1        |        |             |        |                 |        |         |  |

|         | F033<br>F033 |      |              |      | ;<br>CHAIN |                                                                                                                         | ENT         |          |        |             |        |                 |        |         |  |

|         | F033         |      | 31           |      | CHAIN      | •                                                                                                                       | IN          | A. (CH   | ACT)   |             |        | channe          |        |         |  |

|         | F035         |      | -            |      |            |                                                                                                                         | RRCA        | 67 Y 91  |        |             |        | Lecel           | ve che |         |  |

|         | F036         |      |              |      |            |                                                                                                                         | RET         | NC       |        |             |        |                 |        |         |  |

|         | F037         |      |              |      |            |                                                                                                                         | LD          | A + 1    |        |             |        |                 |        |         |  |

|         | F039         |      |              |      |            |                                                                                                                         | OUT         | (CHAC    |        |             |        |                 |        |         |  |

|         | F03B         |      |              |      |            |                                                                                                                         | IN          |          | ACT)   |             | ;      | error           | code   | input   |  |

|         | F03D<br>F03F |      |              |      |            |                                                                                                                         | AND         | 70H      | (@),A  |             |        |                 |        |         |  |

|         | F042         |      |              |      |            |                                                                                                                         | IN          |          | ADT)   |             |        | error<br>charad |        |         |  |

|         | F044         |      |              |      |            |                                                                                                                         | SCF         | H7 ( \$1 |        |             | ,      | charat          | Ler 1  | ιρυι    |  |

|         | F045         |      |              |      |            |                                                                                                                         | RET         |          |        |             |        |                 |        |         |  |

|         | F046         |      |              |      | ;          |                                                                                                                         |             |          |        |             |        |                 |        |         |  |

|         | F046         |      | -            |      | CHBIN      | :                                                                                                                       | ENT         |          |        |             | ;      | channe          | el Bi  | nput    |  |

|         | F046         |      | 33           |      |            |                                                                                                                         | IN          | A,(CH    | (BCT)  |             | ;      | receiv          | ve che | ck      |  |

|         | F048<br>F049 |      |              |      |            |                                                                                                                         | RRCA<br>RET | NC       |        |             |        |                 |        |         |  |

|         | F04A         |      | 1            |      |            |                                                                                                                         | LD          | A+1      |        |             |        |                 |        |         |  |

|         | F04C         |      |              |      |            |                                                                                                                         | OUT         |          | T),A   |             |        |                 |        |         |  |

| 32      | F04E         | DBB  | 33           |      |            |                                                                                                                         | IN          |          | BCT)   |             | ;      | error           | code   | input   |  |

|         | F050         |      |              |      |            |                                                                                                                         | AND         | 70H      |        |             |        |                 |        |         |  |

|         | F052         |      |              |      |            |                                                                                                                         | LD          |          | @),A   |             |        | error           |        |         |  |

|         | F055         |      | 32           |      |            |                                                                                                                         | IN          | A,(CH    | (BDT)  |             | ;      | charad          | ter i  | nput    |  |

|         | F057<br>F058 |      |              |      |            |                                                                                                                         | SCF         |          |        |             |        |                 |        |         |  |

|         | F059         |      |              |      | ;          |                                                                                                                         |             |          |        |             |        |                 |        |         |  |

|         | F059         |      |              |      |            | UTF                                                                                                                     | UT ROL      | JTINE    |        |             |        |                 |        |         |  |

|         | F059         |      |              |      | 5          | (                                                                                                                       | ACC) =      | DATA     | 8      |             |        |                 |        |         |  |

|         | F059         |      |              |      | ;          | <b>T</b> -                                                                                                              |             |          |        |             |        | 1000            |        |         |  |

|         | F059<br>F059 |      |              |      | CHAQU      |                                                                                                                         | PUSH        | AF       |        |             | ;      | channe          | el A d | outoput |  |

|         | F054         |      | 1            |      | AOUT 1     |                                                                                                                         | IN          |          | ACT)   |             | ;      | buffer          | empt   | y check |  |

|         | F05C         |      |              |      |            | ~                                                                                                                       | BIT         | 2 , A    |        |             | 0.00   |                 |        |         |  |

|         | F05E         |      | A            |      |            |                                                                                                                         | JR          | Z + AOL  | T 1    |             |        |                 |        |         |  |

|         | F060         |      |              |      |            |                                                                                                                         | POP         | AF       |        |             |        |                 |        |         |  |

|         | F061         |      | 10           |      |            |                                                                                                                         | OUT         | (CHAI    | T),A   |             | ;      | charad          | ter o  | output  |  |

|         | F063<br>F064 | UУ   |              |      | ;          |                                                                                                                         | RET         |          |        |             |        |                 |        |         |  |

|         | F064         |      |              |      | ,          | т:                                                                                                                      | ENT         |          |        |             | ;      | channe          | el B c | utput   |  |

|         | F064         | F5   |              |      |            | edii 17                                                                                                                 | PUSH        | AF       |        |             | 1982   |                 |        |         |  |

|         | F065         |      |              |      | BOUT1      | :                                                                                                                       | IN          | A, (CH   | BCT)   |             | ;      | buffer          | empt   | y check |  |

|         | F067         |      |              |      |            |                                                                                                                         | BIT         | 2,A      | _      |             |        |                 |        |         |  |

|         | F069         |      | A            |      |            |                                                                                                                         | JR          | Z,BOL    | IT 1   |             |        |                 |        |         |  |

|         | F06B<br>F06C |      | 12           |      |            |                                                                                                                         | POP<br>OUT  | AF       | T) + A |             |        | charad          | ter -  | ut sut  |  |

|         | F06E         |      | · <u>2</u> . |      |            |                                                                                                                         | RET         | VAUDT    | 1770   |             | 7      | - nara(         | LUEP U | JULPUL  |  |

|         | F06F         | - /  |              |      |            |                                                                                                                         | END         |          |        |             |        |                 |        |         |  |

|         |              |      |              |      |            |                                                                                                                         |             |          |        |             |        |                 |        |         |  |

24 ....

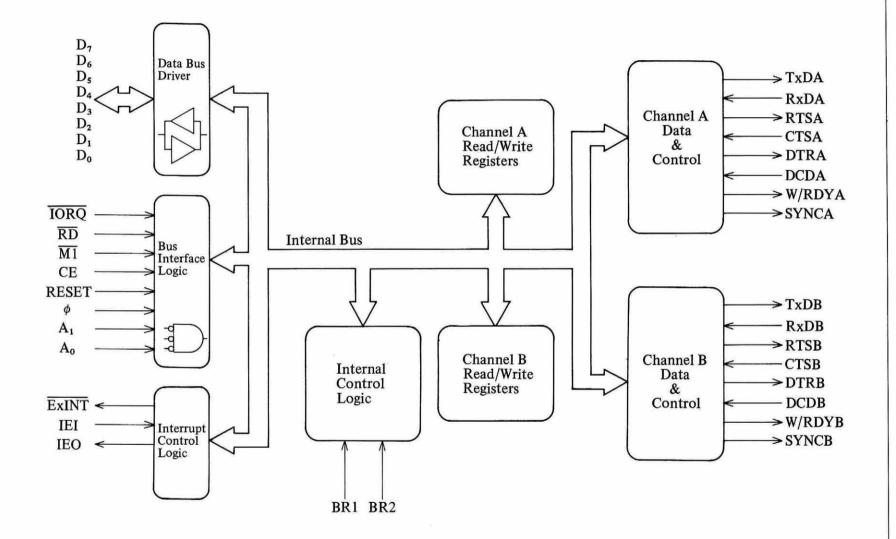

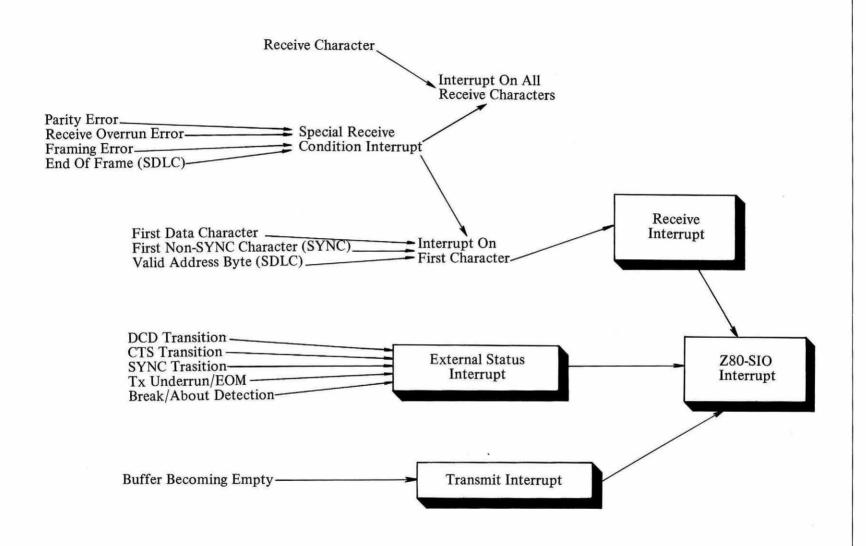

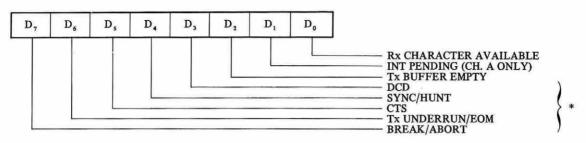

### Interrupts

The following paragraphs describe the use of interrupt between Z80-CPU and the interface card.

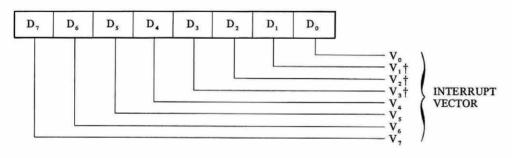

The Z80-SIO offers an elaborate interrupt scheme to provide fast interrupt response in real-time applications. As mentioned earlier, Channel B registers WR2 and RR2 contain the interrupt vector that points to an interrupt service routine in the memory. To service operations in both channels and to eliminate the necessity of writing a status analysis routine, the Z80-SIO can modify the interrupt vector in RR2 so it points directly to one of eight interrupt service routines. This is done under program control by setting a program bit (WR1,  $D_2$ ) in Channel B called "Status Affects Vector." When this bit is set, the interrupt vector in WR2 is modified according to the assigned priority of the various interrupting conditions.

Transmit interrupts, Receive interrupts and External/Status interrupts are the main sources of interrupts (Figure 6-3). Each interrupt source is enabled under program control with Channel A having a higher priority than Channel B, and with Receiver, Transmit and External/Status interrupts prioritized in that order within each channel. When the Transmit interrupt is enabled, the CPU is interrupted by the transmit buffer *becoming* empty. (This implies that the transmitter must have had a data character written into it so it can become empty.) When enabled, the receiver can interrupt the CPU in one of three ways:

- Interrupt on first receive character

- Interrupt on all receive characters

- Interrupt on a Special Receive condition

Interrupt On First Character is typically used with the Block Transfer mode. Interrupt On All Receive Characters has the option of modifying the interrupt vector in the event of a parity error. The Special Receive Condition interrupt can occur on a character or message basis (End Of Frame interrupt in SDLC, for example). The Special Receive condition can cause an interrupt only if the Interrupt On First Receive Character of Interrupt On All Receive Characters mode is selected. In Interrupt On First Receive Character, an interrupt can occur from Special Receive conditions (except Parity Error) after the first receive character interrupt (example: Receive Overrun interrupt).

The main function of the External/Status interrupt is to monitor the signal transitions of the  $\overline{\text{CTS}}$ ,  $\overline{\text{DCD}}$  and  $\overline{\text{SYNC}}$  pins; however, an External/Status interrupt is also caused by a Transmit Underrun condition or by the detection of a Break (Asynchronous mode) or Abort (SDLC mode) sequence in the data stream. The interrupt caused by the Break/Abort sequence has a special feature that allows the Z80-SIO to interrupt when the Break/Abort sequence is detected or terminated. This feature facilitates the proper termination of the current message, correct initialization of the next message, and the accurate timing of the Break/Abort condition in external logic.

Fig. 6-3 Interrupt Structure

26

## 7. Z80-SIO Registers

As mentioned earlier, Z80-SIO incorporated in the hybrid IC has a write register and a read register for each channel.

The bit assignment and functional grouping of each register is configured to simplify and organize the programming process. Table 7-1 illustrates the functions assigned to each read or write register.

| Register | Function                                                                               |

|----------|----------------------------------------------------------------------------------------|

| WR0      | Resister pointers, CRC initialize, initialization commands for the various modes, etc. |

| WR1      | Transmit/Receive interrupt and data transfer mode definition.                          |

| WR2      | Interrupt vector (Channel B only)                                                      |

| WR3      | Receive parameters and controls                                                        |

| WR4      | Transmit/Receive miscellaneous parameters and modes                                    |

| WR5      | Transmit parameters and controls                                                       |

| WR6      | Sync character of SDLC address field                                                   |

| WR7      | Sync character or SDLC flag                                                            |

Table 7-1. Functional Assignments of Read and Write Registers

#### (a) Write Register

| Register | Function                                                             |

|----------|----------------------------------------------------------------------|

| RR0      | Transmit/Receive buffer status, interrupt status and external status |

| RR1      | Special Receive Condition status                                     |

| RR2      | Modified interrupt vector (Channel B only)                           |

#### (b) Read Register

Sinch this interface card is designed exclusively for asynchrounous data communication, it cannot be applied to synchrounous communication.

### Write Registers

The Z80-SIO contains eight registers (WR0–WR7) in each channel that are programmed separately by the system program to configure the functional personality of the channels. With the exception of WR0, programming the write registers requires two bytes. The first byte contains three bits  $(D_0-D_2)$ that point to the selected register; the second byte is the actual control word that is written into the register to configure the Z80-SIO.

Note that the programmer has complete freedom, after pointing to the selected register, of either reading to test the read register or writing to initialize the write register. By designing software to initialize the Z80-SIO in a modular and structured fashion, the programmer can use powerful block I/O instructions.

WR0 is a special case in that all the basic commands  $(CMD_0-CMD_2)$  can be accessed with a single byte. Reset (internal or external) initializes the pointer bits  $D_0-D_2$  to point to WR0.

The basic commands  $(CMD_0-CMD_2)$  and the CRC controls  $(CRC_0, CRC_1)$  are contained in the first byte of any write reigster access. This maintains maximum flexibility and system control. Each channel contains the following control registers. These registers are addressed as commands (not data).

#### (1) WRITE REGISTER 0

WR0 is the command register; however, it is also used for CRC reset codes and to point to the other registers.

| D <sub>7</sub>            | D <sub>6</sub>            | D <sub>5</sub> | <b>D</b> <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do       |

|---------------------------|---------------------------|----------------|-----------------------|----------------|----------------|----------------|----------|

| CRC<br>Reset<br>Code<br>1 | CRC<br>Reset<br>Code<br>0 | CMD<br>2       | CMD<br>1              | CMD<br>0       | PTR<br>2       | PTR<br>1       | PRT<br>0 |

|                           | I                         |                |                       |                |                |                |          |

|                           |                           |                | Control Word          | 1              | R              | legister       | Point    |

#### (1) Pointer Bits $(D_0 - D_2)$

Bits  $D_0 - D_2$  are pointer bits that determine which other write register the next byte is to be written into or which read register the next byte is to be read from. The first byte written into each channel after a reset (either by a Reset command or by the external reset input) goes into WR0. Following a read or write to any register (except WR0), the pointer will point to WR0.

#### Command Bits (D<sub>3</sub>-D<sub>5</sub>)

| Three bits, $D_3 - D_5$ , are encoded to issue the seven basic Z80-SIO cor | Three bits, $D_3 - D_5$ , | are encoded to | issue the seven | basic Z80-SIO | commands. |

|----------------------------------------------------------------------------|---------------------------|----------------|-----------------|---------------|-----------|

|----------------------------------------------------------------------------|---------------------------|----------------|-----------------|---------------|-----------|

| Command | CMD <sub>2</sub> | CMD <sub>1</sub> | CMD <sub>0</sub> |                                       |

|---------|------------------|------------------|------------------|---------------------------------------|

| 0       | 0                | 0                | 0                | Null Command (no effect)              |

| 1       | 0                | 0                | 1                | Send Abort (SDLC Mode)                |

| 2       | 0                | 1                | 0                | Reset External/Status Interrupts      |

| 3       | 0                | 1                | 1                | Channel Reset                         |

| 4       | 1                | 0                | 0                | Enable Interrupt on next Rx Character |

| 5       | 1                | 0                | 1                | Reset Transmitter Interrupt Pending   |

| 6       | 1                | 1                | 0                | Error Reset (latches)                 |

| 7       | 1                | 1                | 1                | Return from Interrupt (Channel A)     |

#### Command 0 (Null)

The Null command has no effect. Its normal use is to cause the Z80-SIO to do nothing while the pointers are set for the following byte.

#### Command 1 (Send Abort)

This command is used only with the SDLC mode to generate a sequence of eight to thirteen 1's.

#### Command 2 (Reset External/Status Interrupts)

After an External/Status interrupt (a change on a modem line or a break condition, for example), the status bits of RR0 are latched. This command re-enables them and allows interrupts to occur again. Latching the status bits captures short pulses until the CPU has time to read the change.

#### Command 3 (Channel Reset)

This command performs the same function as an External Reset, but only on a single channel. Channel A Reset also resets the interrupt prioritization logic. All control registers for the channel must be rewritten after a Channel Reset command.

#### WRITE REGISTER 0

| D, | D <sub>6</sub> | D <sub>5</sub> | D4       | D <sub>3</sub> | D2     | D <sub>1</sub> | Do      | ]                 |

|----|----------------|----------------|----------|----------------|--------|----------------|---------|-------------------|

|    |                |                |          |                | 0      | 0              |         | REGISTER 0        |

|    |                |                |          |                | ŏ      | ŏ              | ĭ       | REGISTER 1        |

|    |                |                | 6        |                | ŏ      | 1              | õ       | <b>REGISTER 2</b> |

|    |                |                |          |                | Õ      | ĩ              | ĩ       | <b>REGISTER 3</b> |

|    |                |                |          |                | 1      | 0              | Õ       | <b>REGISTER 4</b> |

|    |                |                |          |                | 1      | 0              | 1       | <b>REGISTER 5</b> |

|    |                |                |          |                | 1      | 1              | 0       | REGISTER 6        |

|    |                |                |          |                | 1      | 1              | 1       | <b>REGISTER 7</b> |

|    |                | ó              | ó        | ò              | NUL    | L CODE         |         |                   |

|    |                | 0              | 0        | 1              |        |                | T (SDLC | :)                |

|    |                | 0              | 1        | 0              | RESE   | ET EXT/        | STATUS  | INTERRUPTS        |

|    |                | 0              | 1        | 1              | CHA    | NNEL R         | ESET    |                   |

|    |                | 1              | 0        | 0              |        |                |         | XT Rx CHARACTER   |

|    |                | 1              | 0        | 1              |        |                | T PENDI | ING               |

|    |                | 1              | 1        | 0              |        | OR RES         |         |                   |

| 1  |                | 1              | 1        | 1              | RET    | URN FR         | OM INT  | (CH-A ONLY)       |

| 0  | 0              | NUL            | L CODE   |                |        |                |         |                   |

| Õ  | 1              | RESE           | ET Rx C  | RC CHE         | CKER   |                |         |                   |

| 1  | 0              |                |          |                | ERATOF | 2              |         |                   |

| 1  | 1              | RESE           | ET Tx UI | NDERR          | UN/EOM | LATCH          | L .     |                   |

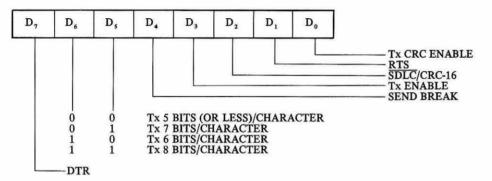

#### WRITE REGISTER 1

#### WRITE REGISTER 2 (CHANNEL B ONLY)

#### **WRITE REGISTER 3**

#### Figure 7-2. Write Register Bit Functions (I)

#### **WRITE REGISTER 4**

| D,               | D <sub>6</sub>   | Ds               | D4                                | D3           | D <sub>2</sub>                       | D1               | Do               | ]                                                         |

|------------------|------------------|------------------|-----------------------------------|--------------|--------------------------------------|------------------|------------------|-----------------------------------------------------------|

|                  |                  |                  |                                   | 0            | 0                                    | 1 ST             | OP BIT/O         | PARITY ENABLE<br>PARITY EVEN/ODD<br>S ENABLE<br>CHARACTER |

|                  |                  |                  |                                   | $1 \\ 1$     | 0<br>1                               | 1½ S<br>2 ST     | OP BITS          | S/CHARACTER<br>/CHARACTER                                 |

|                  |                  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1                  | 16 B<br>SDL  | F SYNC<br>IT SYNC<br>C MODE<br>ERNAL | CHARA<br>(01111) | ACTER<br>110 FLA | G)                                                        |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | x16<br>x32       | LOCK M<br>CLOCK<br>CLOCK<br>CLOCK | MODE<br>MODE |                                      |                  |                  |                                                           |

#### WRITE REGISTER 5

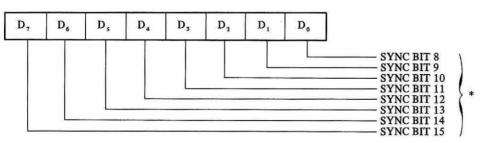

#### WRITE REGISTER 6

\* ALSO SDLC ADDRESS FIELD

#### WRITE REGISTER 7

-

\* FOR SDLC IT MUST BE PROGRAMMED TO "01111110" FOR FLAG RECOGNITION Fig. 7-2 Write Register Bit Functions (II) After a Channel Reset, four extra system clock cycles should be allowed for Z80-SIO reset time before any additional commands or controls are written into that channel. This can normally be the time used by the CPU to fetch the next op code.

#### Command 4 (Enable interrupt On Next Receive Character)

If the Interrupt On First Receive Character mode is selected, this command reactivates that mode after each complete message is received to prepare the Z80-SIO for the next message.

#### Command 5 (Reset Transmitter Interrupt Pending)

The transmitter interrupts when the transmit buffer becomes empty if the Transmit Interrupt Enable mode is selected. In those cases where these are no more characters to be sent (at the end of message, for example), issueing this command prevents further transmitter interrupts until after the next character has been loaded into the transmit buffer or until CRC has been completely sent.

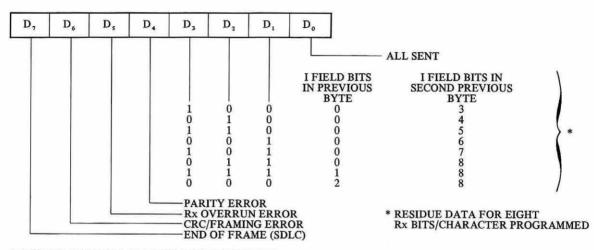

#### Command 6 (Error Reset)

This command resets the error latches. Parity and Overrun errors are latched in RR1 until they are reset with this command. With this scheme, parity errors occurring in block transfers can be examined at the end of the block.

#### Command 7 (Return From Interrupt)

This command must be issued in Channel A and is interpreted by the Z80-SIO in exactly the same way it would interpret an RETI command on the data bus. It resets the interrupt-under-service latch of the highest-priority internal device under service and thus allows lower priority devices to interrupt via the daisy chain. This command allows use of the internal daisy chain even in systems with no external daisy chain or RETI command.

#### $\bigcirc$ CRC Reset Codes 0 and 1 (D<sub>6</sub> and D<sub>7</sub>)

Together, these bits select one of the three following reset command:

| Code 1 $(D_7)$ | Code 0 (D <sub>6</sub> ) | Reset Command                          |

|----------------|--------------------------|----------------------------------------|

| 0              | 0                        | Null Code (no affect)                  |

| 0              | 1                        | Reset Receive CRC Checker              |

| 1              | 0                        | Reset Transmit CRC Generator           |

| 1              | 1                        | Reset Tx Underrun/End Of Message Latch |

The Reset Transmit CRC Generator command normally initializes the CRC generator to all 0's. If the SDLC mode is selected, this command initializes the CRC generator to all 1's. The Receive CRC checker is also initialized to all 1's for the SDLC mode.

#### 33

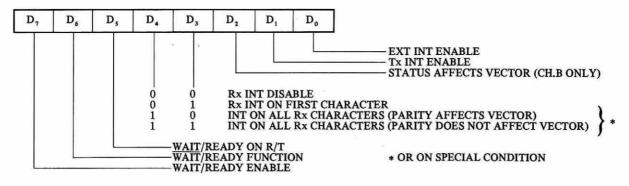

#### (2) WRITE REGISTER 1

WR1 contains the control bits for the various interrupt and Wait/Ready modes.

| D <sub>7</sub>           | D <sub>6</sub>               | D <sub>5</sub>                            | D <sub>4</sub>                 | D <sub>3</sub>                 | D <sub>2</sub>              | <b>D</b> <sub>1</sub>           | Do                               |

|--------------------------|------------------------------|-------------------------------------------|--------------------------------|--------------------------------|-----------------------------|---------------------------------|----------------------------------|

| Wait/<br>Ready<br>Enable | Wait Or<br>Ready<br>Function | Wait/<br>Ready On<br>Receive/<br>Transmit | Receive<br>Interrupt<br>Mode 1 | Receive<br>Interrupt<br>Mode 0 | Status<br>Affects<br>Vector | Transmit<br>Interrupt<br>Enable | External<br>Interrupts<br>Enable |

#### (1) External/Status Interrupt Enable (D<sub>0</sub>)

The External/Status Interrupt Enable allows interrupts to occur as a result of transitions on the  $\overline{\text{DCD}}$ ,  $\overline{\text{CTS}}$  or  $\overline{\text{SYNC}}$  inputs, as a result of a Break/Abort detection and termination, or at the beginning of CRC or sync character transmission when the Transmit Underrun/EOM latch becomes set.

#### **(2)** Transmitter Interrupt Enable $(D_1)$

If enabled, interrupts occur whenever the transmitter buffer becomes empty.

#### ③ Status Affects Vector (D<sub>2</sub>)

This bit is active in Channel B only. If this bit is not set, the fixed vector programmed in WR2 is returned from an interrupt acknowledge sequence. If this bit is set, the vector returned from an interrupt acknowledge is variable according to the following interrupt conditions:

| Channel | V <sub>3</sub> | <b>V</b> <sub>2</sub> | V <sub>1</sub> | Interrupt Conditions        |  |

|---------|----------------|-----------------------|----------------|-----------------------------|--|

| В -     | 0              | 0                     | 0              | Transmit Buffer Empty       |  |

|         | 0              | 0                     | 1              | External/Satus Change       |  |

|         | 0              | 1                     | 0              | Receive Character Available |  |

|         | 0              | 1                     | 1              | Special Receive Condition * |  |

| A       | 1              | 0                     | 0              | Transmit Buffer Empty       |  |

|         | 1              | 0                     | 1              | External/Status Change      |  |

|         | 1              | 1                     | 0              | Receive Character Available |  |

|         | 1              | 1                     | 1              | Special Receive Condition * |  |

#### (4) Receive Interrupt Modes 0 and 1 (D<sub>3</sub> and D<sub>4</sub>)

Together these two bits specify the various character-available conditions. In Receive Interrupt modes 1, 2 and 3, a Special Receive Condition can cause an interrupt and modify the interrupt vector.

| Mode | D4 ReceiveD3 ReceiveInterruptInterruptMode 1Mode 0 |   | Description                                                                              |

|------|----------------------------------------------------|---|------------------------------------------------------------------------------------------|

| 0    | 0                                                  | 0 | Receive Interrupts Disabled                                                              |

| 1    | 0                                                  | 1 | Receive Interrupt On First Character Only                                                |

| 2    | 1                                                  | 0 | Interrupt On All Receive Characters<br>(Parity error is a Special Receive condition)     |

| 3    | 3 1 1                                              |   | Interrupt On All Receive Characters<br>(Parity error is not a Special Receive condition) |

#### **(5)** Wait/Ready Function Selection $(D_5 - D_7)$

The Wait and Ready functions are selected by controlling  $D_5$ ,  $D_6$  and  $D_7$ . Wait/Ready function is enabled by setting Wait/Ready Enable (WR1,  $D_7$ ) to 1. The Ready function is selected by setting  $D_6$  (Wait/Ready function) to 1. If this bit is 1, the WAIT/READY output switches from High to Low when the Z80-SIO is ready to transfer data. The Wait function is selected by setting  $D_6$  to 0. If this bit is 0, the WAIT/READY output is in the open-drain state and goes Low when active.

Both the Wait and Ready functions can be used in either the Transmit or Receive modes, but not both simultaneously. If  $D_5$  (Wait/Ready on Receive/Transmit) is set to 1, the Wait/Ready function responds to the condition of the receive buffer (empty or full). If  $D_5$  is set to 0, the Wait/Ready function responds to the condition of the transmit buffer (empty or full).

| D <sub>7</sub> | D <sub>5</sub>  | D <sub>6</sub> | Selected<br>Functions | Logic States of WAIT/READY Output                                                                                |

|----------------|-----------------|----------------|-----------------------|------------------------------------------------------------------------------------------------------------------|

| 0              |                 | 0              | WAIT                  | Floating (Low when it is active)                                                                                 |

| 0              |                 | 1              | READY                 | High                                                                                                             |

|                | 0<br>(Transmit) | 0              | WAIT                  | Low when transmit buffer is full and an<br>SIO data port is selected.<br>Floating when transmit buffer is empty. |

| 1              |                 | 1              | READY                 | High when transmit buffer is full.<br>Low when transmit buffer is empty.                                         |

| 1              | 1<br>(Receive)  | 0              | WAIT                  | Floating when receive buffer is full.<br>Low when receive buffer is empty and an<br>SIO data port is selected.   |

| (Receive)      | (Receive)       | 1              | READY                 | Low when receive buffer is full.<br>High when receive buffer is empty.                                           |

The logic states of the WAIT/READY output when active or inactive depend on the combination of modes selected. Following is a summary of these combinations:

The WAIT output High-to-Low transition occurs with the delay time  $t_DIC(WR)$  after the I/O request. The Low-to-High transition occurs with the delay  $t_DH\phi(WR)$  from the falling edge of  $\phi$ . The READY output High-to-Low transition occurs with the delay  $t_DL\phi(WR)$  from the rising edge of  $\phi$ . The READY output Low-to-High transition occurs with the delay  $t_DL\phi(WR)$  after  $\overline{IORQ}$  falls.

The Ready function can occur any time the Z80-SIO is not selected. When the  $\overline{\text{READY}}$  output becomes active (Low), the DMA controller issues  $\overline{\text{IORQ}}$  and the corresponding  $B/\overline{A}$  and  $C/\overline{D}$  inputs to the Z80-SIO to transfer data. The  $\overline{\text{READY}}$  output becomes inactive as soon as  $\overline{\text{IORQ}}$  and  $\overline{\text{CS}}$  becomes active. Since the Ready function can occur internally in the Z80-SIO whether it is addressed or not, the  $\overline{\text{READY}}$  output becomes inactive when any CPU data or command transfer takes place. This does not cause problems because the DMA controller is not enabled when the CPU transfer takes place.

The Wait function – on the other hand – is active only if the CPU attempts to read Z80-SIO data that has not yet been received, which occurs frequently when block transfer instructions are used. The Wait function can also become active (under program control) if the CPU tries to write data while the transmit buffer is still full. The fact that the  $\overline{WAIT}$  output for either channel can become active when the opposite channel is addressed (because the Z80-SIO is addressed) does not affect operation of software loops or block move instructions.

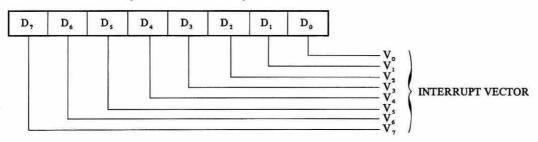

## (3) WRITE REGISTER 2

WR2 is the interrupt vector register; it exists in Channel B only.  $V_4 - V_7$  and  $V_0$  are always returned exactly as written;  $V_1 - V_3$  are returned as written if the Status Affects Vector (WR1, D<sub>2</sub>) control bit is 0. If this bit is 1, they are modified as explained in the previous section.

| D7             | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | $D_2$          | $D_1$          | D <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| V <sub>7</sub> | V <sub>6</sub> | V <sub>5</sub> | V4             | V <sub>3</sub> | V <sub>2</sub> | V <sub>1</sub> | Vo             |

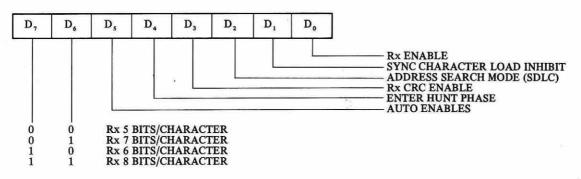

## (4) WRITE REGISTER 3

WR3 contains receiver logic control bits and parameters.

| D <sub>7</sub>              | D <sub>6</sub>              | D <sub>5</sub>  | D <sub>4</sub>         | D <sub>3</sub>            | D <sub>2</sub>            | D <sub>1</sub>               | Do                 |

|-----------------------------|-----------------------------|-----------------|------------------------|---------------------------|---------------------------|------------------------------|--------------------|

| Receiver<br>Bits/<br>Char 1 | Receiver<br>Bits/<br>Char 0 | Auto<br>Enables | Enter<br>Hunt<br>Phase | Receiver<br>CRC<br>Enable | Address<br>Search<br>Mode | Sync Char<br>Load<br>Inhibit | Receiver<br>Enable |

#### (1) Receiver Enable $(D_0)$

A 1 programmed into this bit allows receive operations to begin. This bit should be set only after all other receive parameters are set and receiver is completely initialized.

#### ② Sync Character Load Inhibit (D<sub>1</sub>)

Sync characters preceding the message (leading sync characters) are not loaded into the receive buffers if this option is selected. Because CRC calculations are not stopped by sync character stripping, this feature should be enabled only at the beginning of the message.

#### $\bigcirc$ Address Search Mode (D<sub>2</sub>)

If SDLC is selected, setting this mode causes messages with addresses not matching the programmed address in WR6 or the global (11111111) address to be rejected. In other words, no receive interrupts can occur in the Address Search mode unless there is an address match.

36

#### A Receiver CRC Enable (D<sub>3</sub>)

If this bit is set, CRC calculation starts (or restarts) at the beginning of the last character transferred from the receive shift register to the buffer stack, regardless of the number of characters in the stack.

#### **(5)** Enter Hunt Phase $(D_4)$

The Z80-SIO automatically enters the Hunt phase after a reset; however, it can be re-entered if character synchronization is lost for any reason (Synchronous mode) or if the contents of an incoming message are not needed (SDLC mode). The Hunt phase is re-entered by writing a 1 into bit  $D_4$ . This sets the Sync/Hunt bit ( $D_4$ ) in RR0.

#### 6 Auto Enables (D<sub>5</sub>)

If this mode is selected,  $\overline{\text{DCD}}$  and  $\overline{\text{CTS}}$  become the receiver and transmitter enables, respectively. If this bit is not set,  $\overline{\text{DCD}}$  and  $\overline{\text{CTS}}$  are simply inputs to their corresponding status bits in RR0.

#### $\bigcirc$ Receiver Bits/Characters 1 and 0 (D<sub>7</sub> and D<sub>6</sub>)

Together, these bits determine the number of serial receive bits assembled to form a character. Both bits may be changed during the time that a character is being assembled, but they must be changed before the number of bits currently programmed is reached.

| D <sub>7</sub> | D <sub>6</sub> | Bits/Character |

|----------------|----------------|----------------|

| 0              | 0              | 5              |

| 0              | 1              | 7              |

| 1              | 0              | 6              |

| 1              | 1              | 8              |

## (5) WRITE REGISTER 4

WR4 contains the control bits that affect both the receiver and transmitter. In the transmit and receive intialization routine, these bits should be set before issueing WR1, WR3, WR5, WR6, and WR7,

| D <sub>7</sub> | D <sub>6</sub> | Ds    | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do     |

|----------------|----------------|-------|----------------|----------------|----------------|----------------|--------|

| Clock          | Clock          | Sync  | Sync           | Stop           | Stop           | Parity         | Parity |

| Rate           | Rate           | Modes | Modes          | Bits           | Bits           | Even/          |        |

| 1              | 0              | 1     | O              | 1              | 0              | Odd            |        |

#### 1 Parity (D<sub>0</sub>)

If this bit is set, an additional bit position (in addition to those specified in the bits/character control) is added to transmitted data and is expected in receive data. In the Receive mode, the parity bit received is transferred to the CPU as part of the character, unless 8 bits/character is selected.

#### 2 Parity Even/ $\overline{\text{Odd}}$ (D<sub>1</sub>)

If parity is specified, this bit determines whether it is sent and checked as even or odd (1 = even).

#### $\bigcirc$ Stop Bits 0 and 1 (D<sub>2</sub> and D<sub>3</sub>)

These bits determine the number of stop bits added to each asynchronous character sent. The receiver always checks for one stop bit. A special mode (00) signifies that a synchronous mode is to be selected.

| D3<br>Stop Bits 1 | D <sub>2</sub><br>Stop Bits 0 | Stop Bit                   |  |  |

|-------------------|-------------------------------|----------------------------|--|--|

| 0                 | 0                             | Sync modes                 |  |  |

| 0                 | 1                             | 1 stop bit per character   |  |  |

| 1                 | 0                             | 1½ stop bits per character |  |  |

| 1                 | 1                             | 2 stop bits per character  |  |  |

(4) Sync Mode 0 and 1 ( $D_4$  and  $D_5$ )

These bits select the various options for character synchronization.

| D5<br>Sync Mode 1 | D <sub>4</sub><br>Sync Mode 0 | Sync Mode                         |  |  |  |

|-------------------|-------------------------------|-----------------------------------|--|--|--|

| 0                 | 0                             | 8-bit programmed sync             |  |  |  |

| 0                 | 1                             | 16-bit programmed sync            |  |  |  |

| 1                 | 0                             | SDLC mode (01111110 flag pattern) |  |  |  |

| 1 1               |                               | External Sync mode                |  |  |  |

#### (5) Clock Rate 0 and 1 (D<sub>6</sub> and D<sub>7</sub>)

These bits specify the multiplier between the clock ( $\overline{\text{TxC}}$  and  $\overline{\text{RxC}}$ ) and data rates. For synchronous modes, the x1 clock rate must be specified. Any rate may be specified for asynchronous modes; however, the same rate must be used for both the receiver and transmitter. The system clock in all modes must be at least 4.5 times the data rate. If the x1 clock rate is selected, bit synchronization must be accomplished externally.

| D <sub>7</sub><br>Clock Rate 1 | D <sub>6</sub><br>Clock Rate 0 | Clock Rate                     |  |  |

|--------------------------------|--------------------------------|--------------------------------|--|--|

| 0                              | 0                              | Data Rate x 1 = Clock Rate     |  |  |

| 0                              | 1                              | Data Rate x 16 = Clock Rate    |  |  |

| 1                              | 0                              | Data Rate x $32 = $ Clock Rate |  |  |

| 1                              | 1                              | Data Rate x 64 = Clock Rate    |  |  |

## (6) WRITE REGISTER 5

WR5 contains control bits that affect the operation of transmitter, with the exception of  $D_2$ , which affects the transmitter and receiver.

| D <sub>7</sub> | D <sub>6</sub>        | D <sub>5</sub>        | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub>  | D <sub>1</sub> | Do                  |

|----------------|-----------------------|-----------------------|----------------|----------------|-----------------|----------------|---------------------|

| DTR            | Tx<br>Bits/<br>Char 1 | Tx<br>Bits/<br>Char 0 | Send<br>Break  | Tx<br>Enable   | CRC-16/<br>SDLC | RTS            | Tx<br>CRC<br>Enable |

#### (1) Transmit CRC Enable $(D_0)$

This bit determines if CRC is calculated on a particular transmit character. If it is set at the time the character is loaded from the transmit buffer into the transmit shift register, CRC is calculated on the character. CRC is not automatically sent unless this bit is set when the Transmit Underrun condition exists.

#### **(2)** Request To Sent $(D_1)$

This is the control bit for the  $\overline{\text{RTS}}$  pin. When the  $\overline{\text{RTS}}$  bit is set, the  $\overline{\text{RTS}}$  pin goes Low; when reset,  $\overline{\text{RTS}}$  goes High. In the Asynchronous mode,  $\overline{\text{RTS}}$  goes High only after all the bits of the character are transmitted and the transmitter buffer is empty. In Synchronous modes, the pin directly follows the state of the bit.

#### $\bigcirc$ CRC-16/SDLC (D<sub>2</sub>)

This bit selects the CRC polynomial used by both the transmitter and receiver. When set, the CRC-16 polynomial  $(X^{16} + X^{15} + X^2 + 1)$  is used; when reset the SDLC polynomial  $(X^{16} + X^{12} + X^5 + 1)$  is used. If the SDLC mode is selected, the CRC generator and checker are preset to all 1's and a special check sequence is used. The SDLC CRC polynomial must be selected when the SDLC mode is selected. If the SDLC mode is not selected, the CRC generator and checker are preset to all 0's (for both polynomials).

#### (4) Transmit Enable $(D_3)$